- WSL2全称Windows Subsystem for Linux 2,是微软在Windows 10中推出的一种新的Linux子系统,可以在Windows中运行Linux的二进制文件,同时提供了与Linux相同的系统调用接口,以及与Linux相同的Shell命令行体验。

- IVerilog是一个开源的Verilog仿真器,支持多种平台。IVerilog的仿真速度快,支持多种仿真方式,包括命令行、GUI、VPI等。IVerilog的GUI界面支持波形显示,支持波形的缩放、平移、放大、缩小等操作,支持波形的保存、打印等操作。

安装WSL-Ubuntu22.04

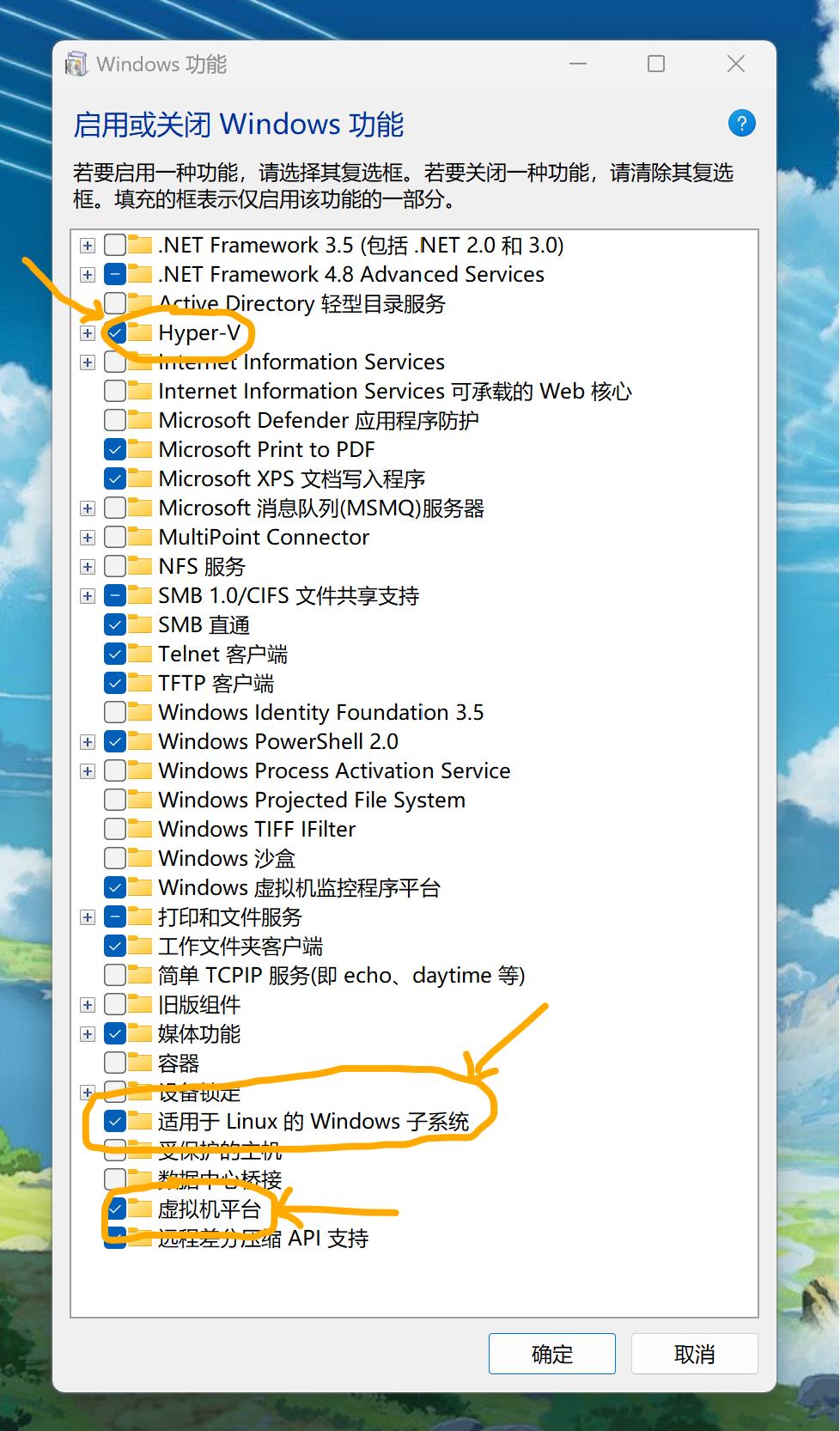

启用Hyper-V、适用于Linux的Windows子系统、虚拟机平台

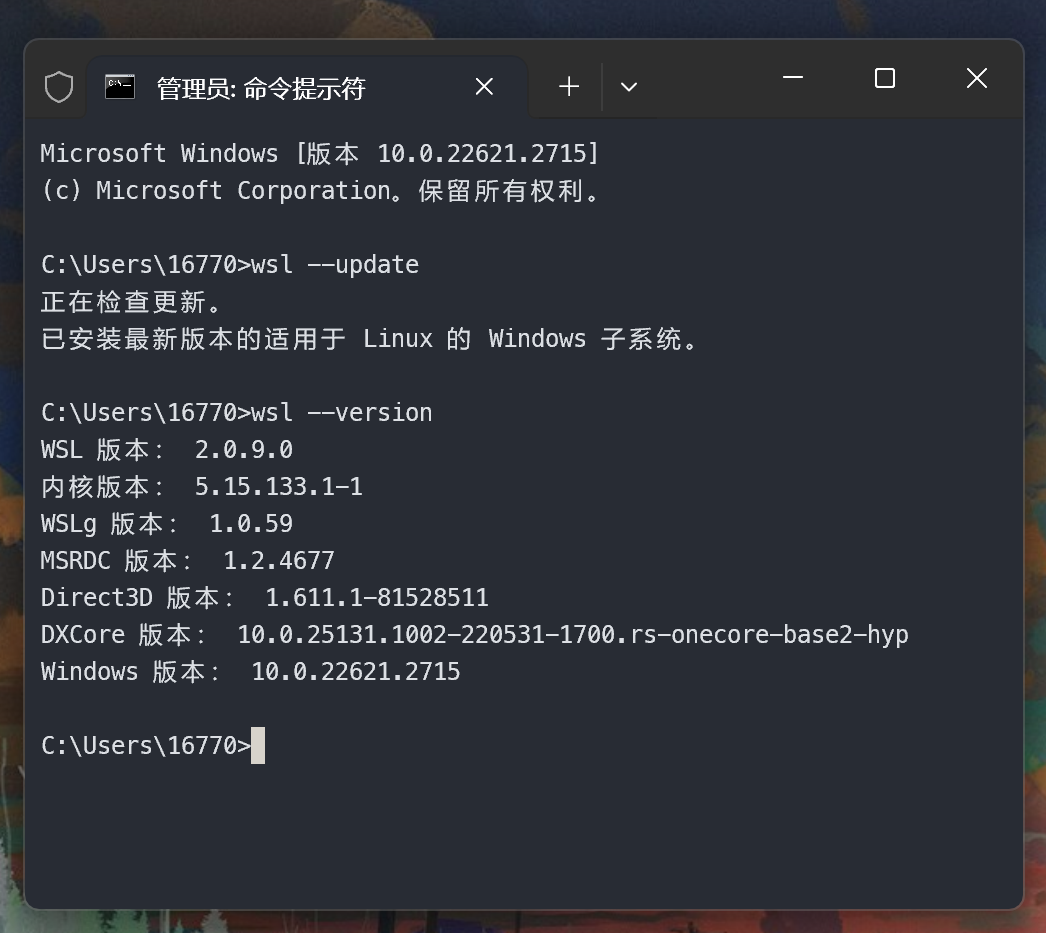

更新WSL版本$ wsl --update$ wsl --version

在Microsoft Store搜索并安装Ubuntu22.04

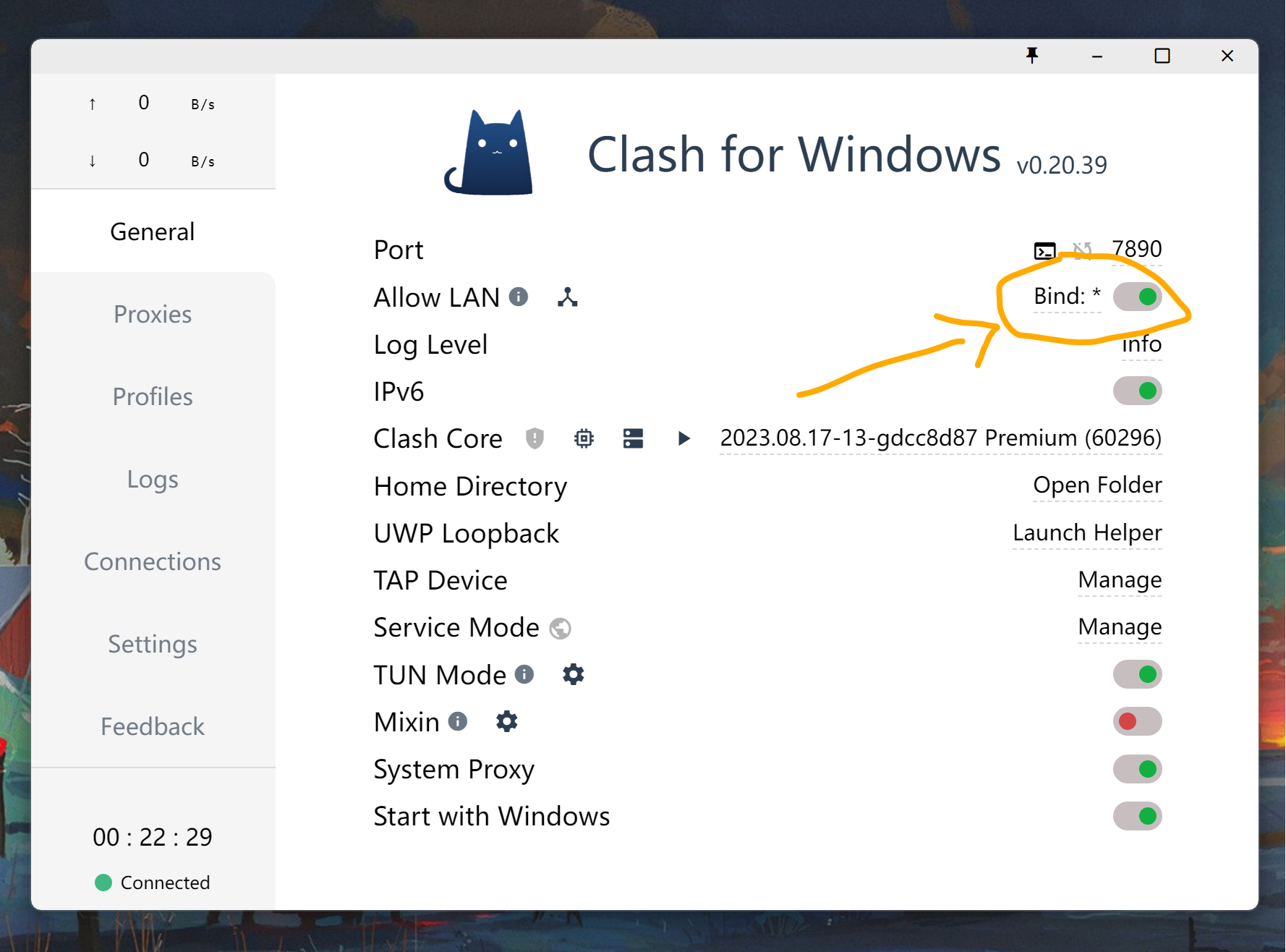

配置clash for windows代理

在clash中启用局域网连接

在WSL中的~/.bashrc中添加代理配置

1 | host_ip=$(cat /etc/resolv.conf |grep "nameserver" |cut -f 2 -d " ") |

更新WSL应用$ sudo apt update$ sudo apt upgrade

安装IVerilog和GTKWave

$ sudo apt install iverilog gtkwave

创建代码文件夹以及用于存放波形wave文件的bin文件夹$ mkdir ~/Verilog-Table && cd Verilog-Table && mkdir bin

在VSCode中打开文件夹$ code .

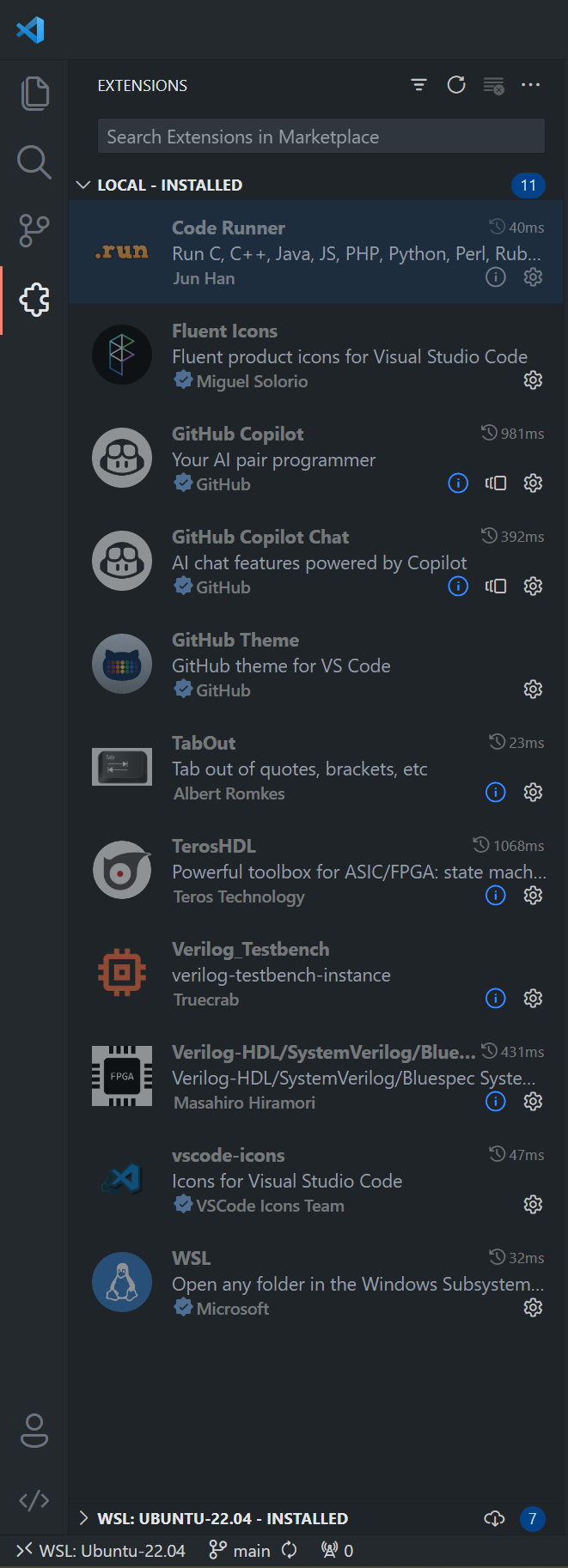

配置VSCode插件

用户配置文件settings.json

1 | { |

在VSCode中选择Snippets: Configure User Snippets配置verilog.json

1 | { |

安装Verible-verilog和ctags

Verible is a suite of SystemVerilog developer tools

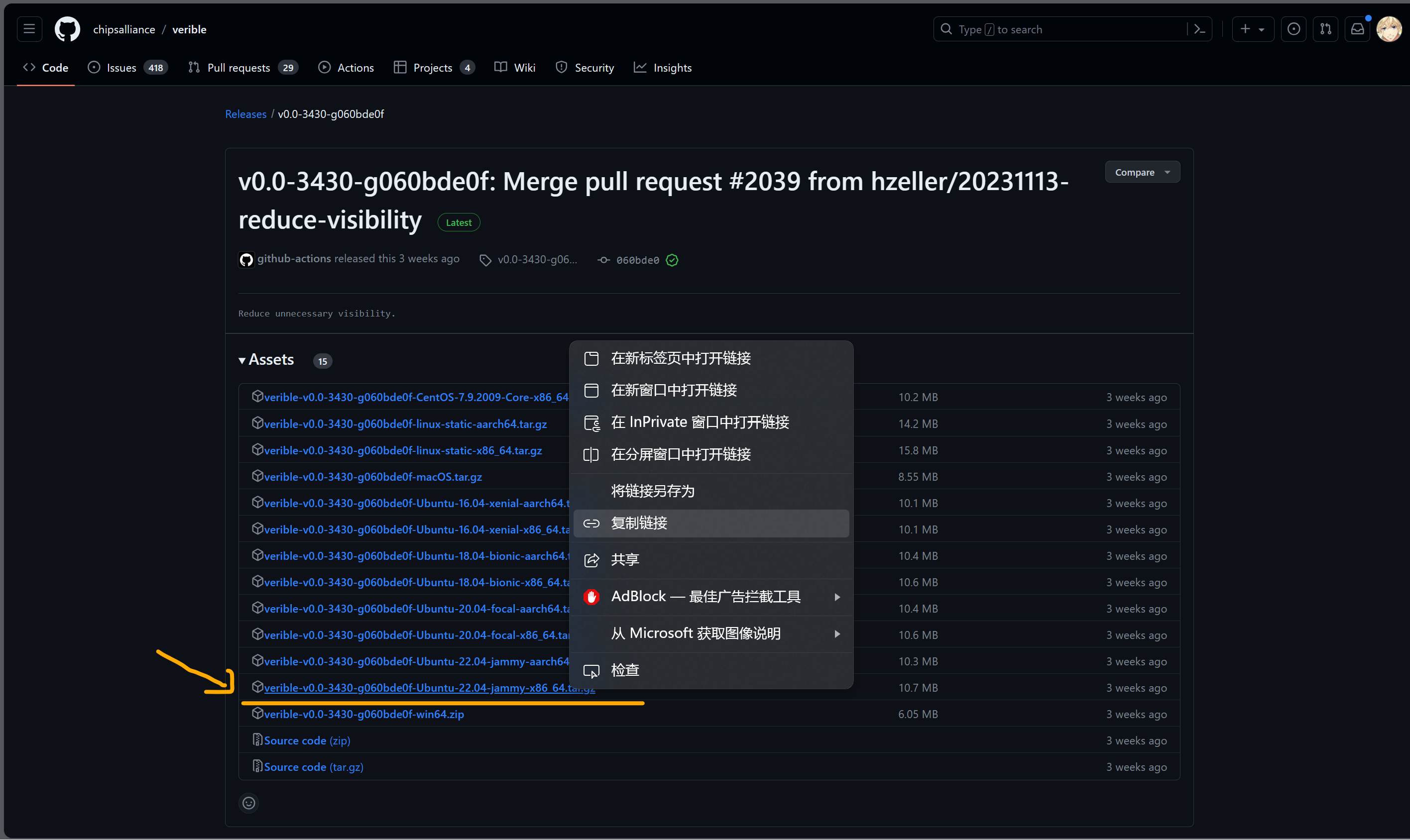

打开Release界面复制下载链接

在WSL使用wget下载$ wget https://github.com/chipsalliance/verible/releases/download/v0.0-3430-g060bde0f/verible-v0.0-3430-g060bde0f-Ubuntu-22.04-jammy-x86_64.tar.gz

使用tar解压$ tar -xvf verible-v0.0-3430-g060bde0f-Ubuntu-22.04-jammy-x86_64.tar.gz

将verible文件夹复制到/usr/local/目录下$ sudo mv verible-v0.0-3430-g060bde0f /usr/local/verible

安装ctags$ sudo apt install universal-ctags

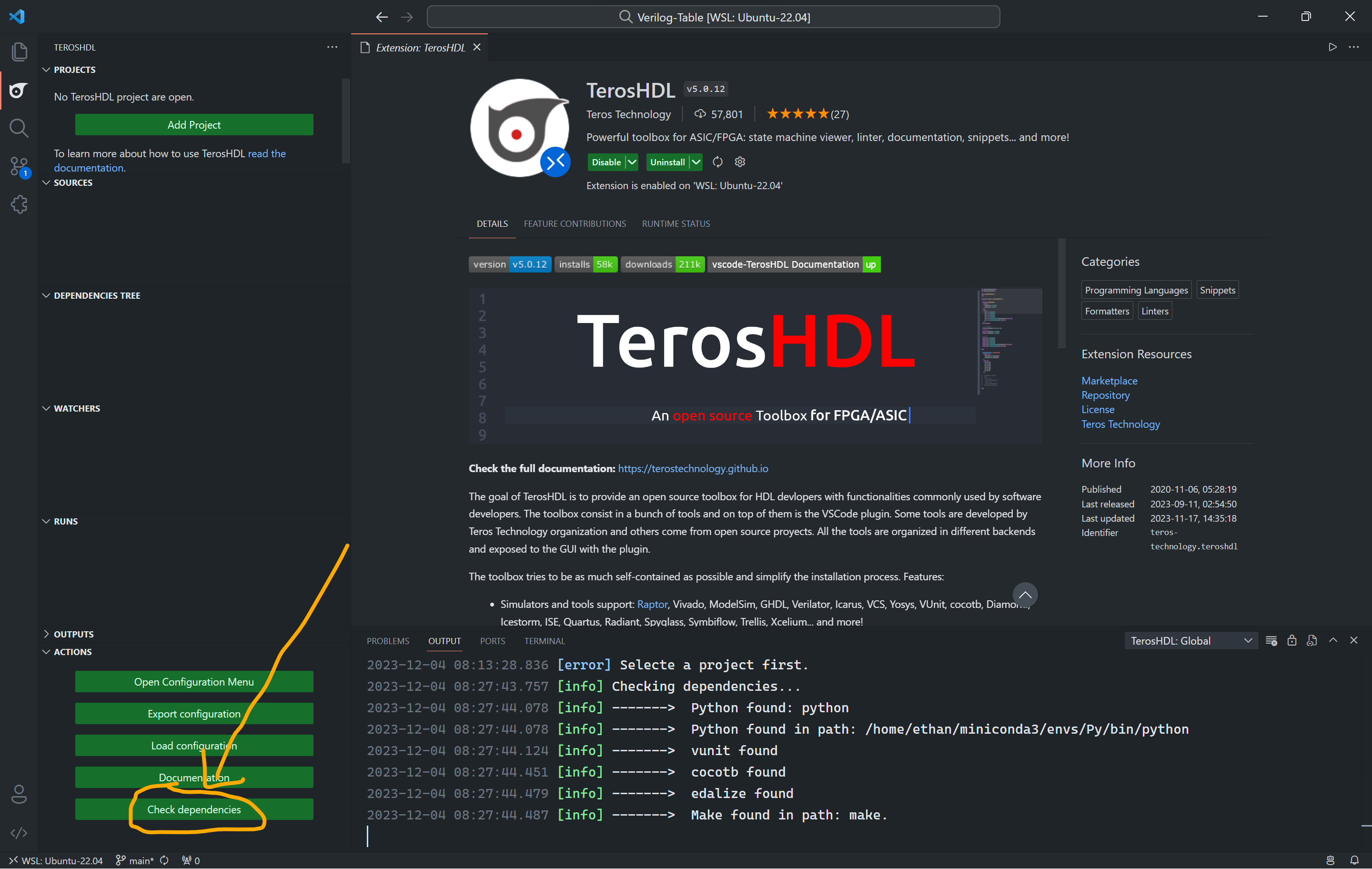

配置VSCode插件TerosHDL

点击Check dependencies查看依赖$ pip install vunit cocotb edalize yowasp-yosys安装

测试配置

解码器代码

1 | module Decode24 ( |

使用Alt+Shift+F通过verible-verilog-format实现代码快速格式化

使用F12通过ctags实现变量定义跳转

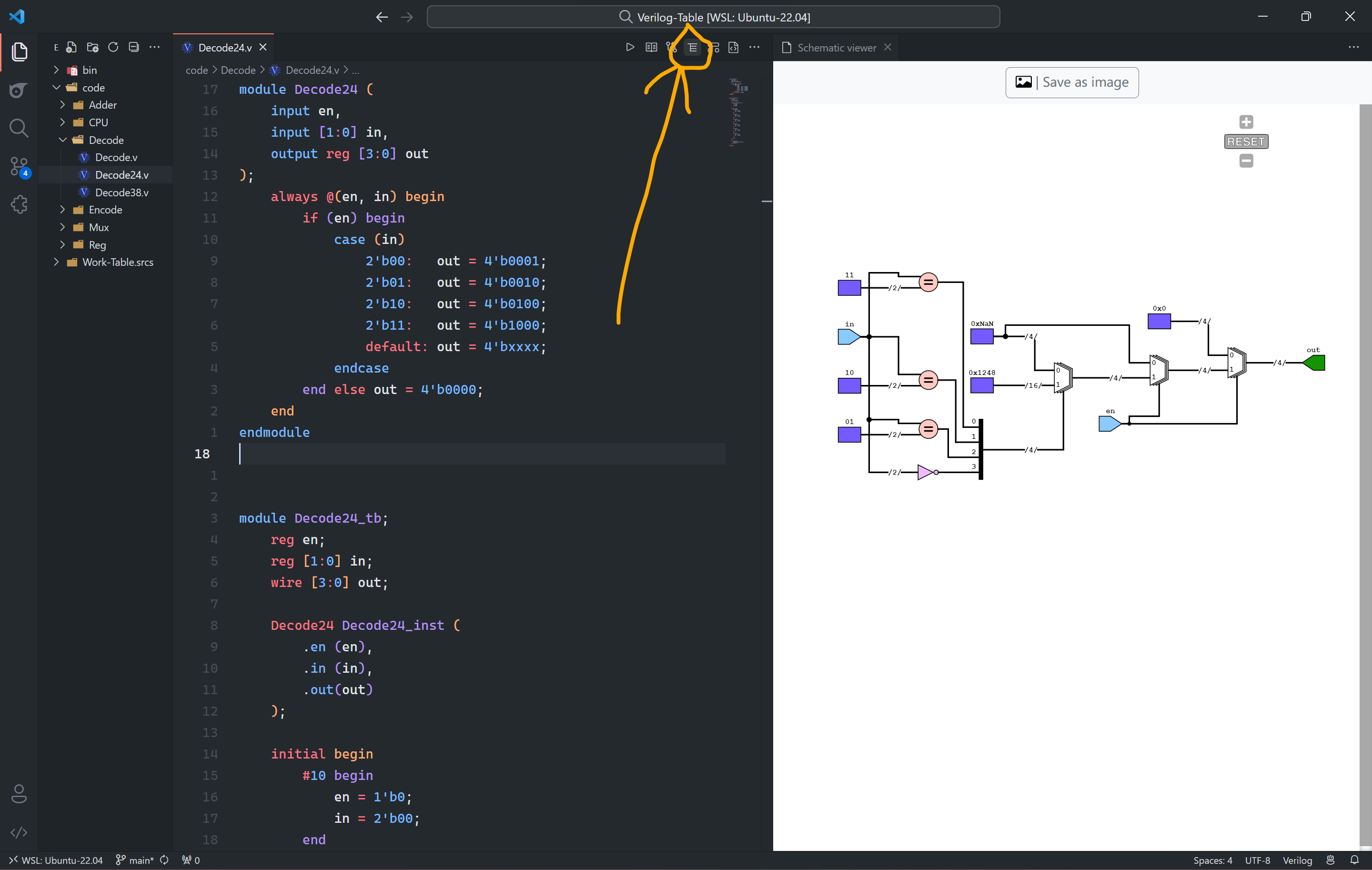

使用TerosHDL查看电路图

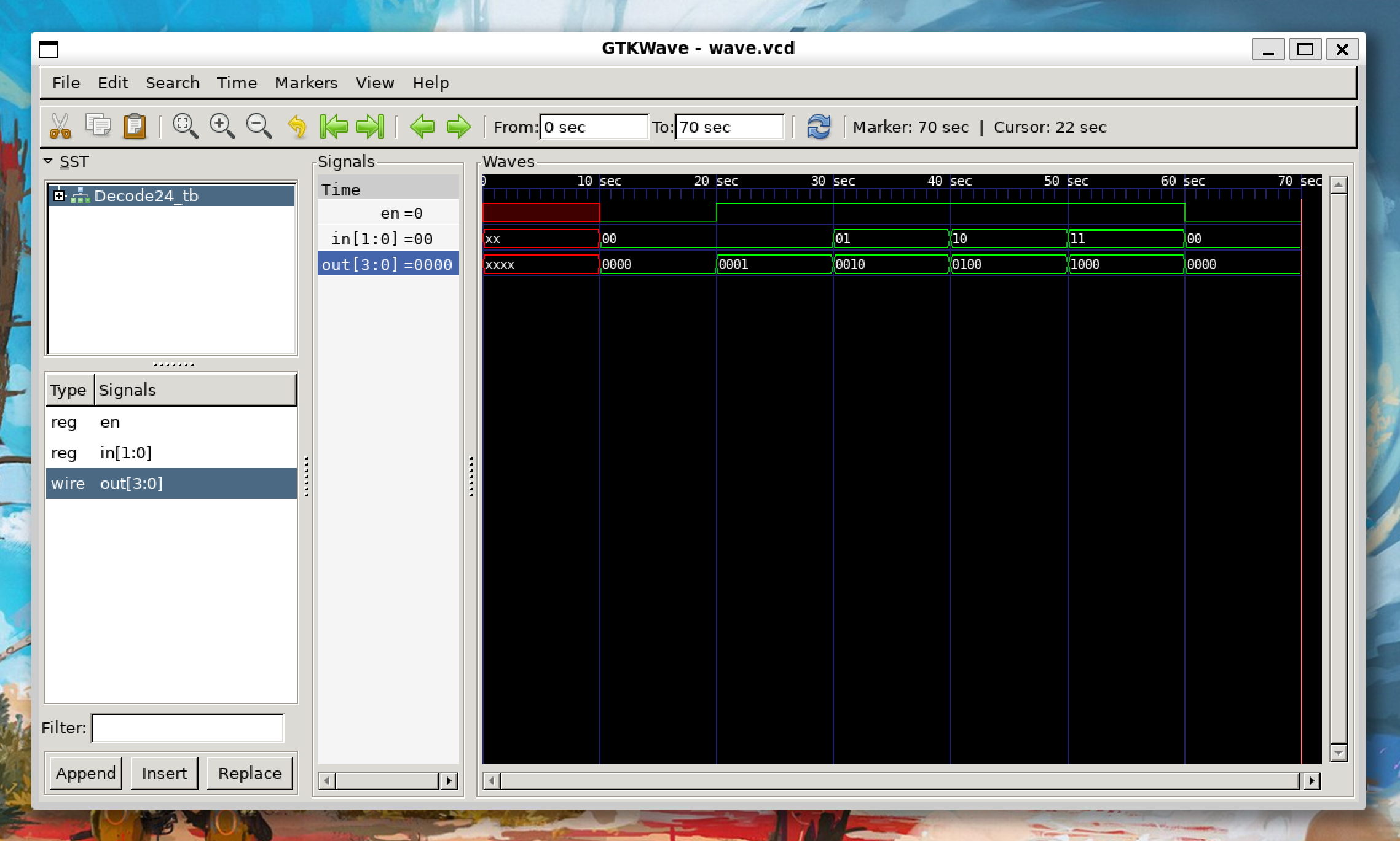

使用Ctrl+Alt+N通过Code-Runner插件执行iVerilog仿真并使用GTKWave查看波形图